Author: sgeorge, Posted on: 10 January 2025 18:57

In the previous entry we were gathering parts, and trying to figure out what steps to take next...

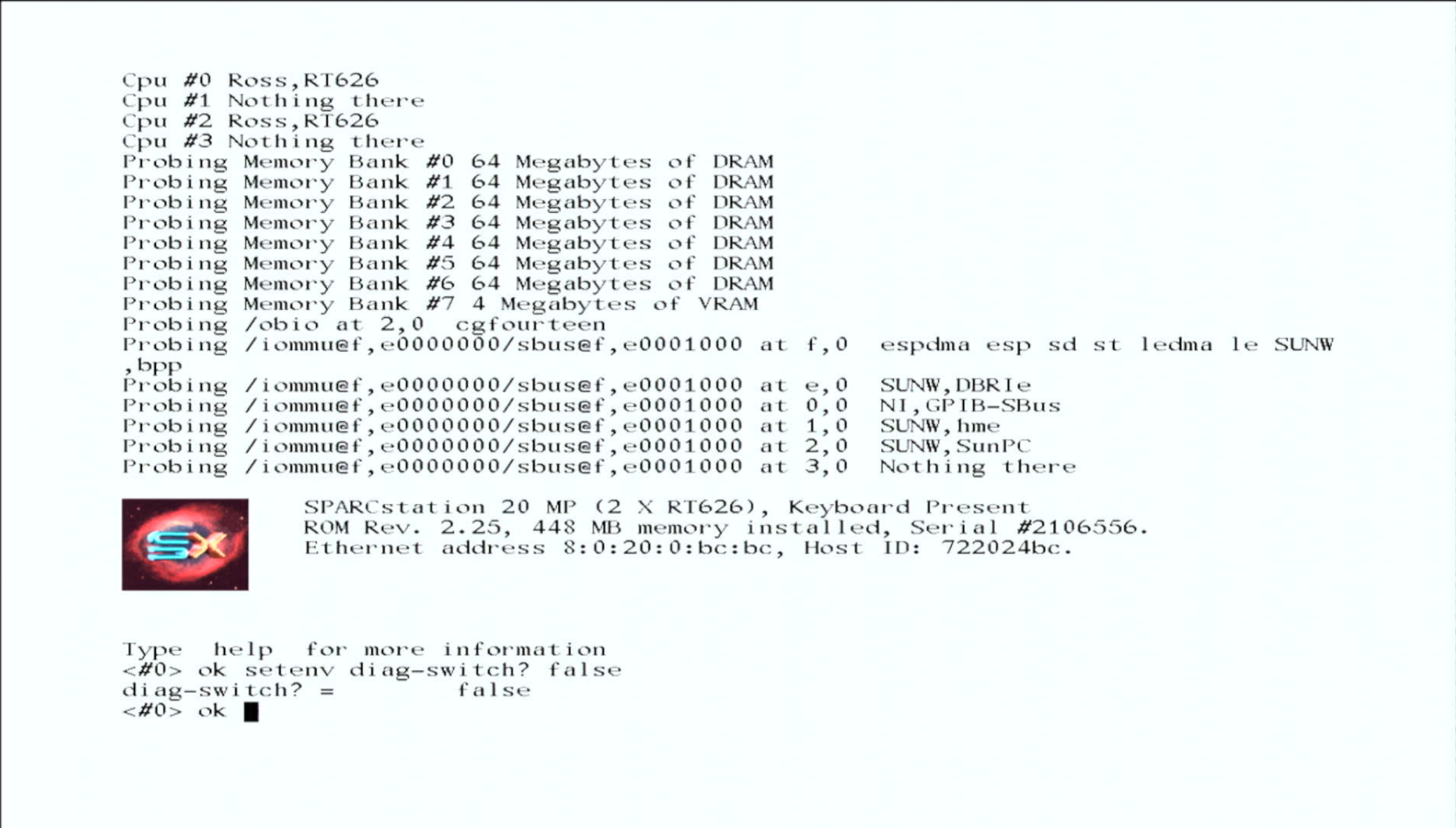

So with NVRAM replaced, and cards added, we get a nice bootup sequence captured from the serial port.

Power-ON Reset

SMCC SPARCstation 10/20 UP/MP POST version VRV3.45 (09/11/95)

CPU_#0 HyperSPARC ROSS RT620/RT626 0x00080000 Bytes ECache

CPU_#2 HyperSPARC ROSS RT620/RT626 0x00080000 Bytes ECache

CPU_#1 ******* NOT installed *******

CPU_#3 ******* NOT installed *******

<<< CPU_00000000 on MBus Slot_00000000 >>> IS RUNNING (MID = 00000008)

HyperSparc Context Pointer Reg Test

HyperSparc Context Reg Test

HyperSparc Root Pointer Reg Test

HyperSparc Instr Pointer Reg Test

HyperSparc Data Pointer Reg Test

HyperSparc Index Tag Reg Test

HyperSparc TLB Replace Reg Test

HyperSparc TLB RAM bit pattern Test

HyperSparc TLB/CAM NTA pattern Test

HyperSparc MMU tlbmiss_test

HyperSparc MMU_tlbhit_test

HyperSparc MMU Flush Tests

HyperSparc Cache RAM W/R Test Ec_size=0x00080000

HyperSparc Cache Tag NTA Test.

HyperSparc ICache RAM Test.

HyperSparc ICache Tag NTA Test.

HyperSparc Write buffer/write-thru mode.

HyperSparc Write buffer/copy-back mode.

HyperSparc Block copy test/mmu_off

HyperSparc Block fill test/mmu_off

HyperSparc Block Copy Test/MMU_ON

HyperSparc Block Fill Test/MMU_ON

EMC/SMC Control Regs Tests

ECC Multiple UE Test

ECC Multiple CE Test

ECC Multiple CE, UE Test

FPU Register File Test

FPU Misaligned Reg Pair Test

FPU Single-precision Tests

FPU Double-precision Tests

FPU SP Invalid CEXC Test

FPU SP Overflow CEXC Test

FPU SP Divide-by-0 CEXC Test

FPU SP Inexact CEXC Test

FPU SP Trap Priority > Test

FPU SP Trap Priority < Test

FPU SP UE Trap Priority Test

FPU DP Invalid CEXC Test

FPU DP Overflow CEXC Test

FPU DP Divide-by-0 CEXC Test

FPU DP Inexact CEXC Test

FPU DP Trap Priority > Test

FPU DP Trap Priority < Test

FPU DP UE Trap Priority Test

FPU DP CE Trap Priority Test

Memory Address Pattern Test

System Interrupt Regs Tests

PROC0 Interrupt Regs Tests

Soft Interrupts OFF Test

Soft Interrupts ON Test

PROC0 User Timer Test

PROC0 Counter/Timer Test

System Counter Test

MSI/MSBI Control Reg Tests

IOMMU CAM NTA Pattern Test

IOMMU TLB NTA Pattern Test

IOMMU CAM TLB Comparator Test

IOMMU TLB Flush Tests

DMA2/MACIO ID Register Test

DMA2/MACIO E_CSR Reg. Test

LANCE Address Port Tests

LANCE Data Port Tests

DMA2/MACIO D_CSR Reg. Test

DMA2/MACIO D_ADDR Reg. Test

DMA2/MACIO D_BCNT Reg. Test

DMA2/MACIO D_NADDR Reg. Test

ESP Registers Tests

DMA2/MACIO P_CSR Reg. Test

DMA2/MACIO P_ADDR Reg. Test

DMA2/MACIO P_BCNT Reg. Test

PPORT Registers Tests

DMA2/MACIO PPORT IO Lpbck Tst

DMA2/MACIO PPORT XFR Lbck Tst

TOD Registers Test

<<< CPU_00000002 on MBus Slot_00000001 >>> IS RUNNING (MID = 0000000a)

HyperSparc Context Pointer Reg Test

HyperSparc Context Reg Test

HyperSparc Root Pointer Reg Test

HyperSparc Instr Pointer Reg Test

HyperSparc Data Pointer Reg Test

HyperSparc Index Tag Reg Test

HyperSparc TLB Replace Reg Test

HyperSparc TLB RAM bit pattern Test

HyperSparc TLB/CAM NTA pattern Test

HyperSparc MMU tlbmiss_test

HyperSparc MMU_tlbhit_test

HyperSparc MMU Flush Tests

HyperSparc Cache RAM W/R Test Ec_size=0x00080000

HyperSparc Cache Tag NTA Test.

HyperSparc ICache RAM Test.

HyperSparc ICache Tag NTA Test.

HyperSparc Write buffer/write-thru mode.

HyperSparc Write buffer/copy-back mode.

HyperSparc Block copy test/mmu_off

HyperSparc Block fill test/mmu_off

HyperSparc Block Copy Test/MMU_ON

HyperSparc Block Fill Test/MMU_ON

EMC/SMC Control Regs Tests

ECC Multiple UE Test

ECC Multiple CE Test

ECC Multiple CE, UE Test

FPU Register File Test

FPU Misaligned Reg Pair Test

FPU Single-precision Tests

FPU Double-precision Tests

FPU SP Invalid CEXC Test

FPU SP Overflow CEXC Test

FPU SP Divide-by-0 CEXC Test

FPU SP Inexact CEXC Test

FPU SP Trap Priority > Test

FPU SP Trap Priority < Test

FPU SP UE Trap Priority Test

FPU DP Invalid CEXC Test

FPU DP Overflow CEXC Test

FPU DP Divide-by-0 CEXC Test

FPU DP Inexact CEXC Test

FPU DP Trap Priority > Test

FPU DP Trap Priority < Test

FPU DP UE Trap Priority Test

FPU DP CE Trap Priority Test

Memory Address Pattern Test

System Interrupt Regs Tests

PROC2 Interrupt Regs Tests

Soft Interrupts OFF Test

Soft Interrupts ON Test

PROC2 User Timer Test

PROC2 Counter/Timer Test

System Counter Test

MSI/MSBI Control Reg Tests

IOMMU CAM NTA Pattern Test

IOMMU TLB NTA Pattern Test

IOMMU CAM TLB Comparator Test

IOMMU TLB Flush Tests

DMA2/MACIO ID Register Test

DMA2/MACIO E_CSR Reg. Test

LANCE Address Port Tests

LANCE Data Port Tests

DMA2/MACIO D_CSR Reg. Test

DMA2/MACIO D_ADDR Reg. Test

DMA2/MACIO D_BCNT Reg. Test

DMA2/MACIO D_NADDR Reg. Test

ESP Registers Tests

DMA2/MACIO P_CSR Reg. Test

DMA2/MACIO P_ADDR Reg. Test

DMA2/MACIO P_BCNT Reg. Test

PPORT Registers Tests

DMA2/MACIO PPORT IO Lpbck Tst

DMA2/MACIO PPORT XFR Lbck Tst

TOD Registers Test

Available Memory 0x1c000000

Allocating SRMMU Context Table

Context Table allocated, Available Memory 0x1bffc000

Setting SRMMU Context Register

Context Table allocated, Available Memory 0x1bffc000

Setting SRMMU Context Table Pointer Register

RAMsize allocated, Available Memory 0x1bfec000

Allocating SRMMU Level 1 Table

Level 1 Table allocated, Available Memory 0x1bfebc00

Mapping RAM @ 0xffef0000

RAM mapped, Available Memory 0x1bfeba00

Mapping ROM @ 0xffd00000

ROM mapped, Available Memory 0x1bfeb800

Mapping ROM @ 0x00000000

ROM mapped, Available Memory 0x1bfeb000

ttya initialized

Cpu #0 Ross,RT626

Cpu #1 Nothing there

Cpu #2 Ross,RT626

Cpu #3 Nothing there

Probing Memory Bank #0 64 Megabytes of DRAM

Probing Memory Bank #1 64 Megabytes of DRAM

Probing Memory Bank #2 64 Megabytes of DRAM

Probing Memory Bank #3 64 Megabytes of DRAM

Probing Memory Bank #4 64 Megabytes of DRAM

Probing Memory Bank #5 64 Megabytes of DRAM

Probing Memory Bank #6 64 Megabytes of DRAM

Probing Memory Bank #7 4 Megabytes of VRAM

Probing /obio at 2,0 cgfourteen

Probing /iommu@f,e0000000/sbus@f,e0001000 at f,0 espdma esp sd st ledma le SUNW,bpp

Probing /iommu@f,e0000000/sbus@f,e0001000 at e,0 SUNW,DBRIe

Probing /iommu@f,e0000000/sbus@f,e0001000 at 0,0 NI,GPIB-SBus

Probing /iommu@f,e0000000/sbus@f,e0001000 at 1,0 SUNW,hme

Probing /iommu@f,e0000000/sbus@f,e0001000 at 2,0 SUNW,SunPC

Probing /iommu@f,e0000000/sbus@f,e0001000 at 3,0 Nothing there

And we get a nice load screen from OpenBoot

So now comes the next task of getting the SCSI2SD setup in there.

tags: SUN, Solaris, Sparcstation, SunOS

(dont include links in your comments.)

The Kråketær is © 2015 - Stu George. -- Static Generator v0.5a